Related past project: High-Speed Serial Link based on 8bit D/A and 4bit A/D converters in 0.25um CMOS technology.

People: W. Ellersick, V. Stojanovic and M. Horowitz (Stanford University)

S. Modjtahedi and C.-K. K. Yang (UCLA)

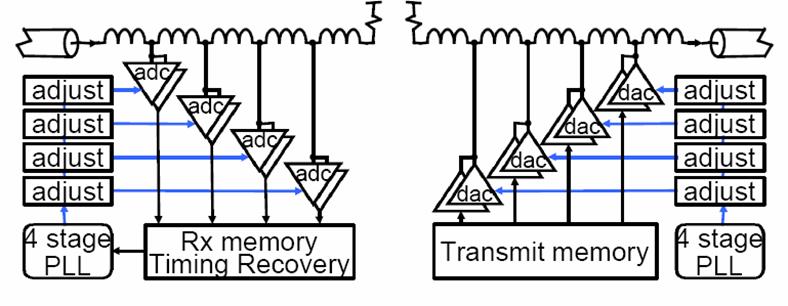

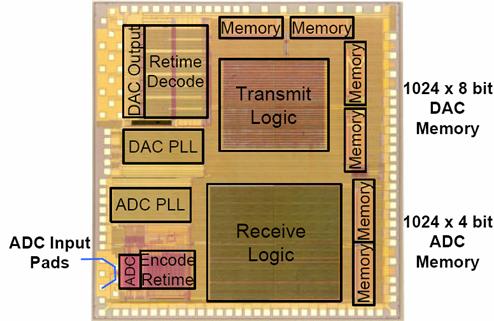

System block diagram Transceiver die photo

Publications:

V. Stojanovic, G. Ginis, M.A. Horowitz "Transmit Pre-emphasis for High-Speed Time-Division-Multiplexed Serial-Link Transceiver," IEEE International Conference on Communications, April 2002.

C.-K.K. Yang, V. Stojanovic, S. Modjtahedi, M.A. Horowitz, W.F. Ellersick "A Serial-Link Transceiver Based on 8GSample/s A/D and D/A Converters in 0.25µm CMOS, IEEE Journal of Solid-State Circuits, vol. 36, no. 11 , pp. 1684-1692, November 2001.

W. Ellersick, V. Stojanovic, M. Horowitz, S. Modjtahedi, C.-K.K. Yang, A Serial-Link Transceiver Based on 8GSample/s A/D and D/A Converters in 0.25µm CMOS, IEEE International Solid-State Circuits Conference, Feb 2001.

W. Ellersick, C.-K. K. Yang, M. Horowitz, W. Dally. GAD: A 12-GS/s CMOS 4-bit A/D converter for an equalized multi-level link, IEEE Symposium on VLSI Ciruits, June 1999

Talks:

- V. Stojanovic, G. Ginis and M. Horowitz. Transmit Pre-emphasis for High-Speed Time-Division-Multiplexed Serial-Link Transceiver. IEEE International Conference on Communications, April 2002.

- Time Division Multiplexing (TDM) must be employed in multi-GSa/s transceivers in order to overcome on-chip clock frequency limitations. This talk describes transmit pre-emphasis filter for a multi-level transceiver making use of TDM. The TDM system is mapped to a MIMO system and the noise sources are analyzed. The design of the pre-emphasis filter is shown to be a non-convex optimization problem. Sub-optimal solutions are derived in closed form and adaptive implementations are described. Simulation results are based on parameters obtained from an experimental testbed.

- W. Ellersick, C-K. K. Yang, V. Stojanovic, S. Modjtahedi and M. A. Horowitz, A Serial Link Transceiver Based on A Serial Link Transceiver Based on 8 GSa GSa/s A/D and D/A Converters /s A/D and D/A Converters in 0.25µm CMOS, IEEE International Solid-State Circuits Conference, Feb 2001.

- This talk presents a transceiver that uses a 4-bit flash analog-to-digital converter (ADC) for the receiver and an 8-bit current-steering digital-to-analog converter (DAC) for the transmitter. Digital compensation reduces the input offset of the ADC comparators to less than 0.6 LSB. 1.1-nH bondwire inductors distribute the parasitic capacitances at the transceiver input and output, reducing attenuation by 10 dB at 4 GHz. Equalization algorithms using the converters compensate for the 1.5-GHz transceiver bandwidth to allow 8-GSamples/s multilevel time-interleaved data transmission