# A Serial Link Transceiver Based on 8 GSa/s A/D and D/A Converters in 0.25µm CMOS

William Ellersick<sup>1,3</sup>, Chih-Kong Ken Yang<sup>2</sup> Vladimir Stojanovic<sup>1</sup>, Siamak Modjtahedi<sup>2</sup>, Mark A. Horowitz<sup>1</sup>

> <sup>1</sup>Stanford University <sup>2</sup>University of California at Los Angeles <sup>3</sup>Analog Devices, Inc.

# Goal: More Bits on Long Links

- Wires expensive: use fewer, more complex links

- Links between boards and systems

- Communications or computing: tens of Gbit/sec

- Up to 10m cables or 1m backplane traces

- CMOS technology for systems-on-a-chip

- Smaller, cheaper, cooler products

- More bits/symbol or faster symbol rate

- Improve and equalize parasitic filters

- Reduce other interference source

This work explores the design of CMOS transceivers for long links, where wires are expensive, so it makes sense to use fewer, more complex links. These links run between communications or computing systems and their boards, carrying tens of Gbit/sec on cables up to 10m long, or over backplane traces up to 1m in length.

CMOS technology is of the most interest, to include links in highly integrated chips along with processors and memory, enabling great reductions in system size, cost and power.

There are only two ways to carry more bits on a link: either pack more bits into each symbol, or run at a faster symbol rate. Either way, parasitic filters must be improved and equalized, and other interference reduced.

- Use high bandwidth circuits and RF techniques

- Linear equalizer using DAC in transmitter

- Wire and circuit losses are linear, time invariant

- Attenuates low frequencies to match cable loss

- Signal amplitudes decrease with frequency

- ADC in receiver for higher performance

- More bits/symbol: multi-level modulation

- Decision Feedback Equalization (DFE)

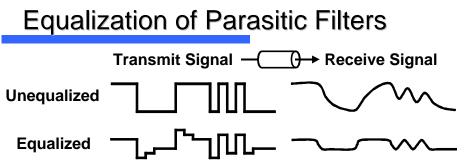

Parasitic filters smear signal edges and prevent them from reaching full swing in a single symbol time. To reduce the filtering, high bandwidth circuits and RF techniques are used. The remaining circuit and wire losses are compensated with adjustable high pass filters called equalizers. A D/A converter in the transmitter and some signal processing are used to implement a linear equalizer. This equalizer emphasizes the high frequency edges of the signal and then decays to a smaller output level. Because the transmitter is limited in voltage swing, the transmit equalizer attenuates low frequency signal components to match the high frequency losses, resulting in a received signal with equal attenuation over frequency.

The use of an A/D converter in the receiver enables digital communications techniques such as multi-level modulation or Decision Feedback Equalization for higher performance.

But even with these techniques, signal amplitudes decrease at higher bit rates.

### Other Interference Reduction

- Correct linear interference with DAC

- Reflections from connectors and packaging

- Signal and clock coupling

- Correlated supply bounce

- Cancel static errors from mismatches

- Timing errors

- DAC nonlinearity

- ADC offset voltage errors

- Random time-varying noise

- Thermal noise

- Random phase noise (high bandwidth timing recovery)

At the same time, other interference sources get worse at higher frequencies. Reflections, coupling and supply bounce are all larger problems with higher bandwidth signals, but can be corrected with the same DAC used to implement the transmit equalizer.

Static interference sources also increase with signaling rates. The signal distortion caused by timing errors increases as signal edge rates increase. Even DAC nonlinearities and ADC offset voltages can be larger for high bandwidth transceivers, because small transistors are used for their low parasitic capacitances. Still, these static interference sources can be corrected.

What remains are the effects of random, time-varying noise processes.

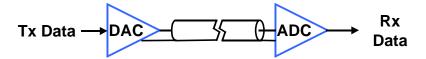

# Calibrated Link Based on DAC, ADC

8 GSample/sec: 1 FO4 gate delay in 0.25µm CMOS 4 GHz Bandwidth

- 2 bits for 4-level signaling

- 2 bits for 4-level signaling

- 4 extra bits for equalization,

2 extra bits for DFE interference correction

- 2 more bits to explore limits

Thus, we envision a calibrated transceiver that measures and corrects for parasitic filters and interference. To increase data capacity, symbol rates are as fast as binary transceivers, which have been reported with bit times of 1 FO4 gate delay. This corresponds to 8 Gsamples/sec in 0.25 um CMOS. Nyquist bandwidth of 4 GHz is desired so the circuits don't limit the link performance.

2 bits of resolution are needed in the transmitter to support 4-level signalling, 4 more bits for equalization and interference correction and an extra 2 bits to explore the limits of resolution. 2 bits are provided in the receiver for 4-level signalling, and 2 more bits for signal processing such as Decision Feedback Equalization.

Now the issue with this architecture is really the performance of the ADC and DAC, not the communication techniques, whose performance is well understood.

## Organization

- Introduction

- →Transceiver design

- DAC circuits

- ADC enhancements

- Inductors to distribute parasitic capacitances

- Clock generation

- Experimental results

- Conclusions

Thus, this paper explores the limits of DAC and ADC performance with sample periods of a gate delay. I will present the circuit design of the DAC, and then the enhancements to the ADC over the first implementation, focusing on how to achieve high bandwidth signal paths through circuit design and the use of inductors to distribute parasitic capacitances.

Then, I'll discuss how precision clocks are generated for the data converters. I will present results from the chips we had fabricated, and conclude the talk.

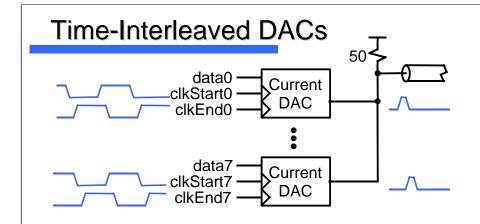

- DACs enabled by overlap of two 1 GHz clocks

- Need precise clocks: 3%<sub>pp</sub> phase noise=>24%<sub>pp</sub> symbol

- Fast clocks (period of 8 gate delays) limit interleaving

- Capacitance of all 8 DACs loads output

In the transmitter, 8 GSample/sec is achieved by time interleaving eight D/A converters, each enabled by phase shifted versions of a 1 GHz clock. Each of the interleaved DACs generates a narrow pulse for one symbol time. The output pulses are summed onto the 25 Ohm impedance formed by the 50 ohm onchip termination in parallel with the 50 ohm transmission line.

Because it's difficult to generate narrow clock pulses, each interleaved DAC is enabled by the overlap of two clocks. The clock edges need to be controlled precisely to produce pulses of desired width and position, since with 8-way time interleaving, 3% of a clock cycle of timing noise corresponds to 24% of a symbol time.

The 1 GHz clocks are about as fast as CMOS clocks can be generated or used. This limits the interleaving required to achieve 8 GSa/s, which is important, because the capacitance of all 8 DACs loads the output.

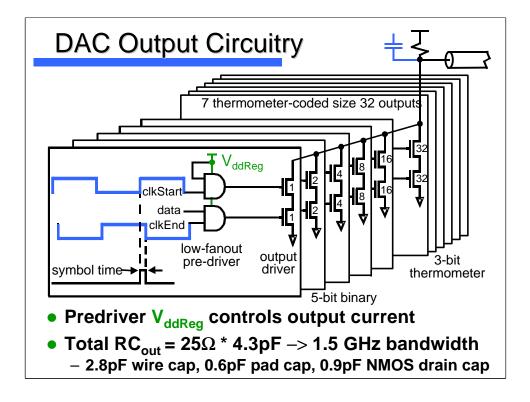

Each of the DACs consists of an array of small current sources, with the least significant bits implemented with 5 binary weighted current sources, and the upper 3 bits with 7 identical current sources. The outputs of the current sources are summed onto the 25 Ohm output impedance.

Each of the current sources consists of 2 stacked NMOS transistors with a grounded source. The output level is controlled by regulating the supply of the predrivers. This maximizes the gate to source voltage at the output, allowing small transistors to be used.

Still, because of the 8 way interleaving, the RC pole at the DAC output limits the bandwidth of the transmitter to 1.5 GHz.

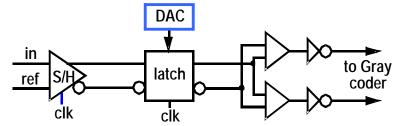

# Interleaved Flash ADC Comparator

- Offsets corrected with DAC in 2nd stage latch

- Simple, high bandwidth sample/hold amplifier

- No switches or capacitors: breaks bandwidth vs. offset tradeoff

- Enhancements over GAD chip (VLSI-99)

- Improved DAC linearity through better matching of clock coupling

- Clocking error corrected

- S/H gain reduced 30% to 1.3: 7 GHz bandwidth (0.4LSB<sub>pp</sub> noise)

- Total RC<sub>in</sub> =  $25\Omega$  \* 1.9pF -> 3.3 GHz bandwidth

- 0.6pF wire cap, 0.6pF pad cap, 0.7pF NMOS gate cap

The ADC is also time interleaved, and uses a flash architecture. Thus, performance is largely determined by the design of the comparator. Offset errors are corrected in the comparator with a DAC that drives a correction signal into the 2nd stage latch. Note that no switches or capacitors are used in the data path. This approach breaks the tradeoff between bandwidth and offset voltage, allowing small transistors to be used for high bandwidth, and correcting for the resultant large transistor mismatch errors. It also allows the use of a simple sample/hold amplifier, with low gain for high bandwidth.

There are several enhancements over the comparator used in the GAD chip. The offset correction DAC linearity is improved through better matching of clock coupling. A clocking error was corrected and the sample/hold gain reduced to increase the sampling bandwidth to 7 GHz. The reduced gain also had the effect of increasing input referred thermal noise to a 6 sigma value of 0.4 LSBpp.

Again, despite the near minimum size devices used, the input capacitance of 1.9pF results in a pole at 3.3 GHz, resulting in ADC bandwidth well short of the 4 GHz goal.

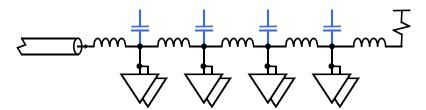

### **ADC Inductor Network**

- Goal: reduce effect of large parasitic capacitance

- Old good idea: distributed amplifiers in oscilloscopes

- If  $sqrt(L/C)=50\Omega$ : lumped transmission line

- Each ADC sees  $50\Omega$  to the right,  $50\Omega$  to the left

- Inputs of pairs of ADCs to separate pads

- Bond wire inductors can optionally be inserted

- Bandwidth traded for delay (100ps total on line)

So we use an old, good idea, used for years to build distributed amplifiers in oscilloscopes. By dividing up the large capacitances, and inserting the right value of inductor, a lumped 50 ohm transmission line is constructed.

Pairs of interleaved ADC inputs are wired to separate pads. This allows bond wire inductors to optionally be inserted between the input capacitances to evaluate performance with and without the inductors.

This distributed ADC technique trades bandwidth for delay - about 100 ps down the entire LC line. A block diagram of the full transceiver shows how this delay is managed.

# Transceiver Inductors and Clocking Adjust A stage PLL Rx memory PLL Transmit memory Transmit memory Rx memory PLL Transmit memory Transmi

- Phase adjusters correct LC delay, static errors

- Adjuster: clock mux, 1/16th-symbol clock interpolator

- 8 ADC phase adjusters + 1 for timing recovery

- 16 DAC phase adjusters (2 clocks for each DAC)

The receiver is shown on the left. Because each time-interleaved A/D converter has its own clock (shown in blue), the LC delay on the lumped transmission line is compensated for by adjusting the phase of these clocks. The same ability to adjust clock phases is needed to cancel static phase errors, which have dominated timing errors in previous transceiver chips.

To produce adjustable clocks, a four-stage differential PLL drives 8 clocks that are nominally 45 degrees apart, into the phase adjusters, each of which consists of a clock mux to select two adjacent clock phases, and a digitally controlled clock interpolator with a resolution of 1/16th of a symbol time. One phase adjuster is used for each of the eight time-interleaved ADCs to correct for the LC delays and for static phase errors. An additional phase adjuster in the feedback path of the receive PLL is used for clock recovery.

A similar inductor network is used to distribute the transmitter output capacitance, with two phase adjusters for each interleaved DAC to correct pulse width and pulse position.

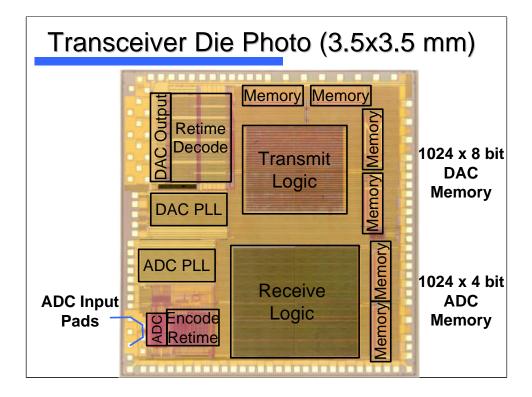

This represents the bulk of the circuitry on the test chip, so let's take a look at the layout.

The PLLs can clearly be seen in this die photo, swollen by the large number of phase adjusters and the big devices used to reduce clock buffering. The analog ADC circuitry is quite small, even though it includes 120 comparators and the offset correction circuits and memory. Its output is converted to 4 bit Gray code, retimed to a lower rate clock, and fed into a synthesized logic block, which either stores or compares the data against the contents of a 1024 symbol memory.

The transmit data path is similar but reversed. Data from a 1024 symbol memory is retimed to the high speed DAC clocks and decoded. Again, the analog output circuitry is fairly small, even though most of the design effort and experimental work focused on the analog sections.

Measured ADC results are presented first, comparing performance with and without inductors. Note the four input pads in the lower left, each of which is connected to a pair of time-interleaved ADCs. These can either be bonded with short, flat bond wires with no appreciable inductance as shown, or with small inductor coils to distribute the input capacitance. Let's zoom in on these input pads...

### **ADC Bond Wire Inductor Photo**

- 2-turn inductors ~1.1 nH

- Not onchip inductors: large R

- Goal: inductors in flip-chips

- HSPICE: +/-30% variation doesn't affect results

- nH/mm depends on log(D)

- 30 gauge wire form: 200 μm

- Verify LC match with TDR

... on a chip bonded with inductors. Each of the inductors consists of a 2-turn coil of bond wire. The input comes in to the first ADC input pad, through a 2-turn bond wire inductor to the second input pad, through more inductors to the third and fourth input pads, and through a final inductor to the onchip termination resistor. Now this is a beautiful piece of bonding work by Pauline Prather, who works in our lab, but it is obviously not mass manufacturable. Bond wire inductors were used instead of onchip spiral inductors to keep series resistance low, with the goal to gather data to help design inductors into a flip chip package. Precise 1.1nH inductors obviously cannot be bonded, but simulation shows that a 30% variation in inductance is acceptable. Also, because the inductance per unit length depends on the log of physical dimensions, moderate changes in shape and size only result in small changes in the inductance value. To control the diameter of the coils, we looked for the smallest cylinder we could find, which turned out to be a piece of 30 gauge wire, and used it as a form to wind inductors with a 200 um diameter. The LC matching was verified with a Time Domain Reflectometer, showing that the ADC input capacitance has been distributed, so that the frequency response of the ADC should be limited only by the sample/hold bandwidth of 7 GHz.

- Inductors increase bandwidth to more than 6 GHz

- Measured TDR matches simulated TDR with L=1.1nH

- Bumps are due to connector and package reflections

And indeed, the ADC has a measured bandwidth of more than 6 GHz with inductors, compared to 3.5 GHz without. The measured data on the left is generated by driving asynchronous sine waves into the ADC and fitting ideal sine waves to the data captured in the onchip memory. The frequency response matches the simulation of a detailed model of the ADC input path, shown on the right. Three values of inductance are simulated to indicate the insensitivity of the results to inductance value.

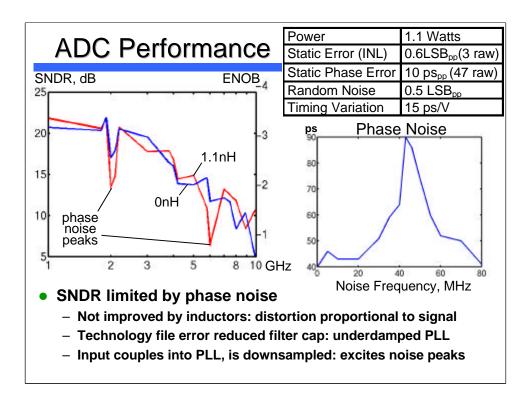

Now these results looks very promising, and show that the ADC has high input bandwidth, but we need to consider a broader measure of ADC performance that includes noise and distortion.

The Signal to Noise and Distortion ratio of the ADC is plotted on the left, showing a resolution bandwidth of only about 3 GHz. This is due to phase noise, which causes distortion that increases with frequency and is proportional to the sampled signal. Inductors do not improve the SNDR, because the larger received signal with inductors is accompanied by an increase in distortion.

The large phase noise is due to an error in the layout technology file that caused the PLL filter capacitance to be less than half the desired value. Simulations show this results in an underdamped PLL, and this is confirmed by experimental measurements showing a peak of 90 ps of jitter,pp in response to noise at 42 MHz, even though the PLL was designed for a loop bandwidth of 12 MHz.

Coupling from the single-ended ADC input to the PLL reference clock is downsampled by the PLL, exciting the phase noise peak at input frequencies near clock harmonics, and can be seen in the SNDR plot.

The ADC consumes a little over 1 Watt, dominated by the oversized PLL and phase adjusters. Offset correction using the DACs in each comparator reduces errors from 3 to 0.6 LSBpp. The phase adjusters reduce static errors from 47 to 10 ps,pp. Half an LSB of p-p random noise is measured, matching estimates of thermal noise. Sample time variation is 15 ps/V, or about 11 ps over the 750 mV input range of the ADC.

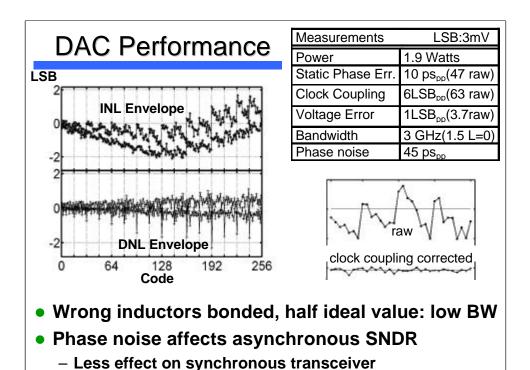

The DAC dissipates about twice as much power as the ADC, because it has twice as many clocks. With a 750mV output range, the 8-bit DAC has an LSB of 3 mV. Coupling from all the interleaved clocks is large, but is reduced from 67 to 6 LSBpp by transmitting a correction signal as shown on the right, albeit at the cost of a reduction in usable output swing. Voltage errors due to transistor mismatches and output nonlinearity are reduced from 3.7 to 1 LSBpp after calibration, as seen in the envelope plots on the left that show the worst case INL and DNL out of the eight time-interleaved DACs, at each output code. The large DNL errors every 16th code fortunately are negative, and thus cause overlapping codes instead of large gaps. Therefore, they do not increase errors after calibration, which are determined by the distance to the closest possible output voltage. Thus, the DAC has about 5 effective bits at low frequencies after calibration. Resolution at higher frequencies is limited by phase noise and by the 3 GHz output bandwidth, which is low because inductors of half the ideal value were mistakenly bonded.

However, phase noise affects synchronous operation less than it affects the SNDR and effective number of bits, so let's equalize and characterize the transceiver in a link.

Measured with MSB comparators by adding DC

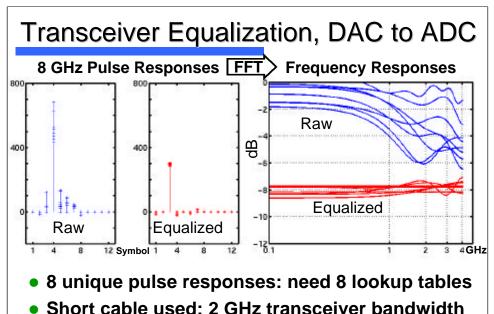

Parasitic filtering causes transceiver pulses to be spread over several symbol times, as seen in the data samples from the A/D converter on the left. The pulses? have varying heights due to residual pulse width variations between the time-interleaved DACs, and have varying intersymbol interference due to differing positions on the lumped LC transmission lines. Thus, each transmitter needs a unique equalization lookup table. However, this does not increase complexity, since parallel lookup tables are already needed to run at 8 GSa/s. After equalization and gain correction, the pulse heights are nearly the same, and the interference in adjacent symbol times is significantly smaller. Only a short cable was used in this experiment, as the transceiver bandwidth of 2 GHz presents a good challenge to 8 Gsymbol data transmission.

The FFT of the sampled pulse responses shows equalization in the frequency domain. By attenuating low frequency signal components, the transmit equalizer produces a received signal that is evenly attenuated over frequency.

To avoid quantization errors in equalization, the pulse responses are measured by adding a varying DC voltage to the signal to find the switching point of the most significant bit comparator in each time-interleaved A/D converter.

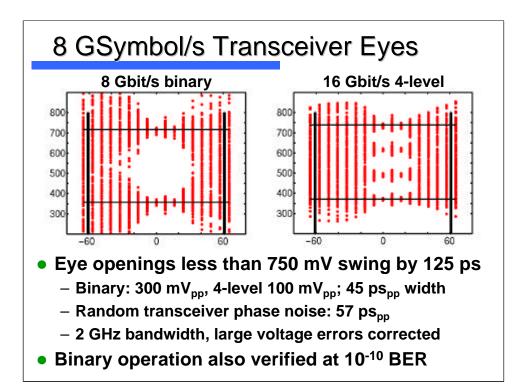

A similar technique is used to measure the voltage and phase margins of the link. The schmoo plots shown here are generated by varying the DC voltage and the phase of the receiver clocks, and plotting a dot where bit errors are recorded. Eye openings are less than the 750 mV signal swing and 125 ps symbol time, but can still support 4-level signalling. The received signal swing is reduced by the 2 GHz bandwidth, and by clock coupling correction. Performance is limited by the random transceiver phase noise of 57 ps,pp, but binary operation was still verified at a bit error rate of 10^-10.

Thus, despite large phase and voltage errors and significant clock coupling and bandwidth limitations, an accurate 8 GSymbol/s transceiver can be built in 0.25 um CMOS.

### Conclusion

- High speed CMOS circuit techniques

- Time-interleave DACs and ADCs for high sample rate

- Inductors to trade bandwidth for delay

- Small transistors for high bandwidth, low power

- Calibration to improve accuracy, maintain speed

- Extra DAC bits to correct interference, nonlinearity

- ADC offset cancellation with DAC inside comparator

- Clock interpolators to correct static phase errors

- Correct layout, circuit asymmetries to lower design risk

- Data converters at binary transceiver speeds

- Accurate timing is crucial

- Long links: 4-level signaling, DFE

In conclusion, we've demonstrated techniques for designing high performance circuits in cheap CMOS technology. High sample rate is achieved by time-interleaving D/A and A/D converters. High bandwidth is achieved by using inductors to trade bandwidth for delay, and by designing with small transistors for their low parasitics and low power consumption.

Calibration techniques are used to improve accuracy while maintaining speed. Extra DAC resolution corrects for interference and simple nonlinearities, and ADC offsets are corrected with a DAC inside each comparator. Timing accuracy is improved with clock interpolators to correct static phase errors. These techniques also correct for layout and circuit asymmetries and thus lower design risk. This was crucial, because we learned more than we ever expected to on this project. But we were able to use calibration techniques to correct most of the mistakes that we learned from.

This work demonstrates that data converters are possible at binary transceiver speeds, and that accurate timing is crucial to their operation. As circuit speeds increase and transistors become cheaper, data converters will enable the use of digital communications techniques for even higher speed links.

I would like to acknowledge the assistance of Ken Chang, Azita Emami, Dean Liu and Jackie Wong, and some amazing bonding by Pauline Prather. Finally, this work would not have been possible without the efforts of the students I followed, particularly that of Stefanos

|                                                                                  | 1/31/01 |

|----------------------------------------------------------------------------------|---------|

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

|                                                                                  |         |

| A Serial Link Transceiver Based on 8 GSa/s A/D and D/A Converters in 0.25μm CMOS | S 20    |