Project:

Limits of Electrical Signaling Modeling, Analysis and Design of High-Speed

Links

Student:

Vladimir Stojanovic

Supported by: MARCO Interconnect Focus Center and Rambus, Inc.

Project Description, Publications,

Talks, Bibliography

and Related Past Project

The focus of this project is to understand the limiting factors to the increase in data rate of high-speed electrical links.

The advances in design of high-speed link components, most dominantly high-speed transmitters and receivers, and precise timing and data recovery loops, have made the link circuitry on a chip so fast that now the problem is in the limited bandwidth of the wires connecting the chips. We analyze the signal degradation and magnitude and dynamics of different noise sources that are present in the system. This analysis yields the projections about the capacity of electrical interconnects and also practical achievable data rates.

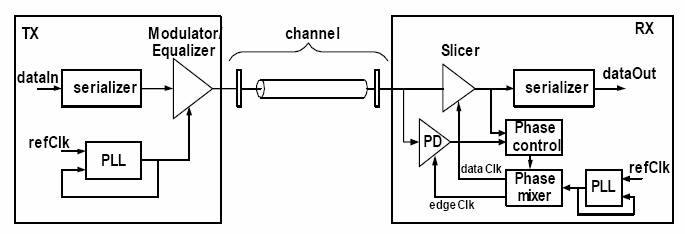

Typical system level view of a high-speed serial link is shown in Fig. 1.

Fig. 1. System view of a typical high-speed serial link

This work is an attempt to bridge the gap between high-speed link design and high-speed communication system design. We apply analysis and measurement techniques used in communication system design to the unique problems posed by high-speed channel-limited link design. By analyzing the specific properties of the high-speed link system, and by classifying and analyzing the noise sources, we are able to decide where communication techniques can be applied most cost effectively and how to apply them.

Since practical high-speed links have many design constraints, it is very important to understand the most critical effects and focus the system and circuit design to these most sensitive issues. We created the statistical modeling and analysis tool to ease the decision making process in design of high-speed link systems, under very low BER constraints. These low BER constraints require specially accurate modeling of noise sources and system dynamics.

In this project, we focus on the example application in backplane serial-links.

Fig. 2. Backplane serial-link environment

Backplane serial-link environment suffers from severe bandwidth limitations and discontinuities, which both lead to significant signal degradation in GHz range, due to inter-symbol interference (ISI). Backplane interconnects, although time-invariant, vary significantly in channel characteristics even within the same backplane, depending on the characteristics of the channel components Fig. 2. Channel variations and dispersion effects of inter-symbol interference, Fig. 3.

Fig. 3. Frequency response of different channels within a backplane (left), inter-symbol interference due to bandwidth limitations of the wires (right), 160ps symbol time

While fundamental thermal voltage noise in

high-speed link systems is very small, the biggest challenge is in modeling the

timing noise in the link that originates from the phase-locked loop (PLL)

circuits and data-recovery loops (CDR). We developed techniques for mapping the

timing noise to effective voltage noise, in order to estimate the relative

importance of different noise sources to the BER of the link [1,2].

The most dominant component of jitter in PLLs is from

power supply noise, hence part of our research has

been related to developing the supply noise measurement

and characterization techniques.

Modeling of the behavior and noise dynamics of the bang-bang CDR loops is also a significant challenge, since these loops are nonlinear. Using Markov chain analysis we were able to characterize basic response of bang-bang CDR loops to the noise and interference in the receiver signal. Phase state model and associated phase probability distribution are shown in Fig. 4.

Fig. 4. Markov model of bang-bang CDR loop (left) and its steady-state phase distribution (right)

Putting all the system components and noise together, we are able to estimate the sensitivity of the link performance to different link design specifications. One of the outputs of the tool are the BER contour plots which indicate the remaining system margins at a target BER, due to signal degradation and noise, Fig. 5.

Fig. 5. BER contour plot, 6.25Gb/s link with 5taps of linear equalization (left) and extra tap of DFE (right)

During the course of this project we developed system architectures [3] and algorithms for link equalization [2,4], and both binary and multi-level signaling. We use transmit pre-emphasis to compensate for dispersion effects and restricted range decision-feedback equalization to eliminate long-latency reflections, Fig. 6.

Fig. 6. Link equalization system architecture [3]

Feedback equalization is very hard in high-speed links, since in current technology and todays data rates, the loop latency is usually several symbol long, limiting the range of the feedback equalization. To overcome this effect and improve link performance we recently implemented a 1-tap DFE using loop unrolling in the receiver and adequate adaptation and CDR techniques, [1].

Fig. 7. Immediate tap DFE using loop unrolling, [1]

In addition to improving the data rates of todays baseband systems, we also use our noise and system models to predict the limits of high-speed electrical links. Channel capacity is estimated in Fig. 8, for best and worst backplane channels in the presence of thermal termination noise, and phase noise of the LC and ring oscillator based PLLs.

Fig. 8. Capacity limits of backplane channels in the presence of thermal and phase noise [2].

Future work on this project focuses on several issues. First direction is in bridging the gap between todays high-speed link based on baseband modulation techniques, and capacity results. Second task is the work on design of very precise circuits and calibration techniques that would allow multi-level signaling and increased spectral efficiency. Third direction is better modeling and analysis of synchronization techniques and their impact on link performance.

V. Stojanović, A. Ho, B. Garlepp,

F. Chen, J. Wei,

A. Ho, V. Stojanović, F. Chen, C. Werner, G. Tsang, E. Alon, R. Kollipara, J. Zerbe, M.A. Horowitz, Common-Mode Backchannel Signaling System for Differential High-speed Links, submitted to IEEE Symposium on VLSI Circuits, June 2004.

E. Alon, V. Stojanović, M.A. Horowitz, Circuits and Techniques for High-Resolution Measurement of On-Chip Power Supply Noise, submitted to IEEE Symposium on VLSI Circuits, June 2004.

V. Stojanovic, A. Amirkhany and M. Horowitz, Optimal Linear Precoding with Theoretical and Practical Data Rates in High-Speed Serial-Link Backplane Communication, accepted for publication at IEEE International Conference on Communications, June 2004.

J. Zerbe, C. Werner, V. Stojanovic, F. Chen, J. Wei, G. Tsang, D. Kim, W. Stonecypher, A. Ho, T. Thrush, R. Kollipara , M. Horowitz, K. Donnelly, Equalization and Clock Recovery for a 2.5 - 10Gb/s 2-PAM/4-PAM Backplane Transceiver Cell," IEEE Journal of Solid-State Circuits, Dec. 2003.

V. Stojanovic, M. Horowitz, Modeling and Analysis of High-Speed Links, IEEE Custom Integrated Circuits Conference, September 2003. (invited)

J. Zerbe, C. Werner, V. Stojanovic, F. Chen, J. Wei, G. Tsang, D. Kim, W. Stonecypher, A. Ho, T. Thrush, R. Kollipara , M. Horowitz, K. Donnelly, Equalization and Clock Recovery for a 2.5 - 10Gb/s 2-PAM/4-PAM Backplane Transceiver Cell, IEEE International Solid-State Circuits Conference, Feb. 2003.

V. Stojanovic, G. Ginis, M.A. Horowitz, Transmit Pre-emphasis for High-Speed Time-Division-Multiplexed Serial-Link Transceiver, IEEE International Conference on Communications, April 2002.

- V. Stojanovic and M. Horowitz. Modeling and Analysis of High-Speed Links. IEEE Custom Integrated Circuits Conference, September 2003.

- This invited talk presents the analysis of noise sources, both in voltage and timing, in a high-speed link system and their impact on the choice and effectiveness of different communication techniques. We show that the dominant noise sources are colored and bounded, as opposed to standard unbounded Gaussian white noise assumptions. With very low BER requirements, shape of noise probability distributions and their correlations are much more important than just their total power, which contrasts the standard analysis in communication systems.

- V. Stojanovic, G. Ginis and M. Horowitz. Transmit Pre-emphasis for High-Speed Time-Division-Multiplexed Serial-Link Transceiver. IEEE International Conference on Communications, April 2002.

- Time Division Multiplexing (TDM) must be employed in multi-GSa/s transceivers in order to overcome on-chip clock frequency limitations. This talk describes transmit pre-emphasis filter for a multi-level transceiver making use of TDM. The TDM system is mapped to a MIMO system and the noise sources are analyzed. The design of the pre-emphasis filter is shown to be a non-convex optimization problem. Sub-optimal solutions are derived in closed form and adaptive implementations are described. Simulation results are based on parameters obtained from an experimental testbed.